Before moving on the “VLSI Design Cycle”, let’s see what is the meaning of VLSI. It(VLSI) stands for “Very Large-Scale Integration” which means that millions or billions of components like transistors, capacitors, registers, diode will be integrated on a single chip. By using those components , we can generate a very complex design such as CPU, RAM, ROM, etc.

That’s the reason VLSI is one of the toughest fields to learn. We need to develop a good understanding of it because it needs in-depth knowledge of electronics.

In VLSI, technologies change as frequently as every few years. The reason behind this is that every sector has a large number of data. So processing such large data reqires more time will be more . Hence fast processing is necessary. To increase processing power, semiconductor industry keeps on modifying new rules and technology in VLSI domain. But some sets of rules will almost remain same, even the VLSI product design process will remain same.

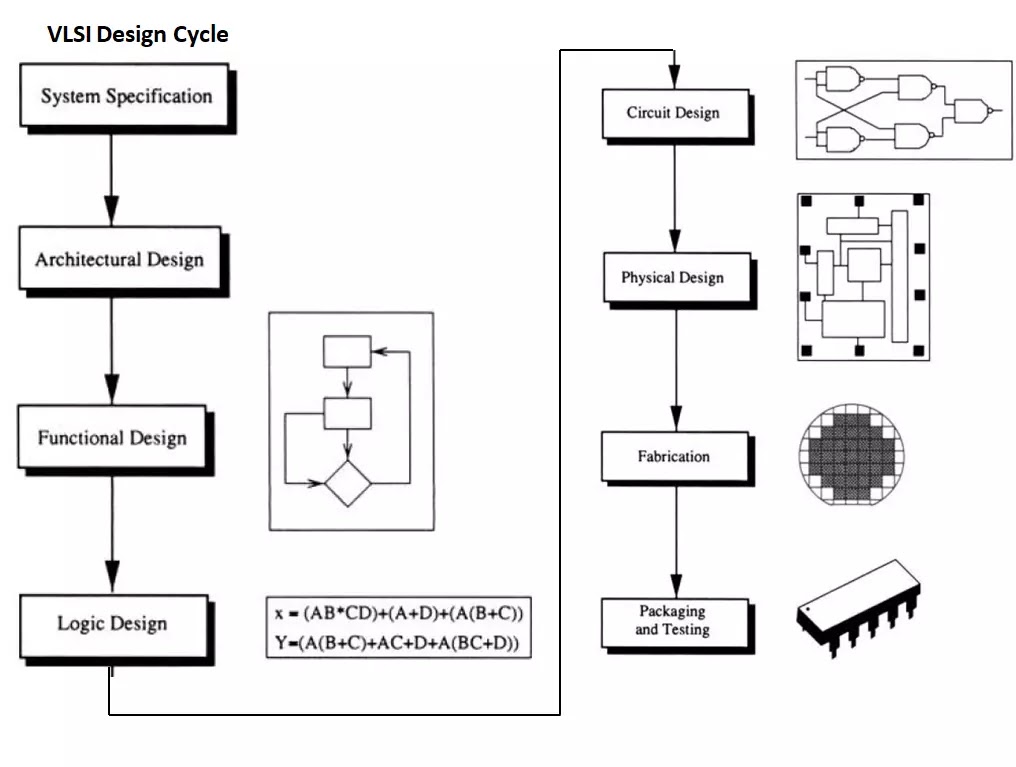

So in this article, we will learn “the design flow of VLSI” which will elaborate us about the design process of a VLSI product from specification to fabrication, packaging and testing.

1.1 System Specification:

The first step of any design process is to lay down the specifications of the system

- System specification is a high-level representation of the system.

- The factors to be considered in this process include performance, functionality, and physical dimensions (size of the die (chip)).

- The fabrication technology and design techniques are also considered.

- The specification of a system is a compromise between market requirements, technology and economical viability.

- The end results are specifications for the size, speed, power, and functionality of the VLSI system.

1.2 Architectural Design:

Design of the basic architecture of the system such as RISC(Reduced Instruction Set Computer) versus CISC (Complex Instruction Set Computer), number of ALUs, Floating Point units, number and structure of pipelines, and size of caches among others.

- The outcome of architectural design is a textual (English-like) description of a Micro-Architectural Specification (MAS).

- Architects can accurately predict the performance, power and die size of the design based on such a description.

- Such estimates are based on the scaling of existing designs or components of existing designs.

- Early estimates are critical to determining the viability of a product for a market segment.

- For example, for mobile computing (such as laptop computers), low power consumption is a critical factor, due to limited battery life. Early estimates based on architecture can be used to determine if the design is likely to meet its power spec.

1.3 Behavioral or Functional Design:

Main functional units of the system, the interconnect requirements between the units are identified.

- The area, power, and other parameters of each unit are estimated.

- The behavioral aspects of the system are considered without implementation-specific information. For example, it may specify that multiplication is required, but exactly in which mode such multiplication may be executed is not specified.

- May use a variety of multiplication hardware depending on the speed and word size requirements.

- Specify behavior, in terms of input, output and timing of each unit, without specifying its internal structure.

- The outcome is usually a timing diagram or other relationships between units Functional or behavioral design provides quick emulation of the system and allows fast debugging of the full system.

- Behavioral design is largely a manual step with little or no automation help available.

1.4 Logic Design:

The control flow, word widths, register allocation, arithmetic operations, and logic operations of the design that represent the functional design are derived and tested. This description is called Register Transfer Level (RTL) description.

- RTL is expressed in a Hardware Description Language (HDL), such as VHDL or Verilog.

- This description can be used in simulation and verification.

- This description consists of Boolean expressions and timing information.

- The Boolean expressions are minimized to achieve the smallest logic design which conforms to the functional design.

- This logic design of the system is simulated and tested to verify its correctness.

- In some special cases, logic design can be automated using high-level synthesis tools. These tools produce an RTL description from a behavioral description of the design.

Boolean Logic

A = (XY + YZ)(X + Z) + (Z + XY) B = (X + YZ) + (XY + Z)(Z + X)

1.5 Circuit Design:

To develop a circuit representation based on the logic design.

- The Boolean expressions are converted into a circuit representation by taking into consideration the speed and power requirements of the original design.

- Circuit Simulation is used to verify the correctness and timing of each component.

- The circuit design is usually expressed in a detailed circuit diagram.

- This diagram shows the circuit elements ( cells, gates, transistors ) and interconnection between these elements.

- This representation is also called a netlist.

- Tools used to manually enter such descriptions are called schematic capture tools.

- In many cases, a netlist can be created automatically from logic (RTL) description by using logic synthesis tools.

1.6 Physical Design:

The circuit representation (or netlist) is converted into a geometric representation of the circuit which is called a layout.

- The layout is created by converting each logic component (cells, macros, gates, transistors) into a geometric representation (specific shapes in multiple layers), which performs the intended logic function of the corresponding component.

- Connections between different components are also expressed as geometric patterns typically line in multiple layers.

- The exact details of the layout also depend on design rules, which are guidelines based on limitations of the fabrication process and electrical properties of the fabrication materials.

- Physical design is a very complex process and is usually broken down into various sub-steps.

- Various verification and validation checks are performed on the layout during physical design.

- Physical design can be completely or partially automated and layout can be generated directly from netlist by Layout Synthesis tools.

1.7 Fabrication:

After layout and verification, the design is ready for fabrication. Since layout data is typically sent to fabrication on a tape, the event of a release of data is called Tape Out.

- Layout data is converted (or fractured) into photo-lithographic masks, one for each layer. Masks identify spaces on the wafer, where certain materials need to be deposited, diffused, or even removed.

- Silicon crystals are grown and sliced to produce wafers.

- The fabrication process consists of several steps involving deposition, and diffusion of various materials on the wafer.

- During each step, one mask is used.

- Before the chip is mass-produced, a prototype is made and tested.

- The industry is rapidly moving towards a 30 cm (12 inch) wafer allowing even more chips per wafer leading to lower cost per chip.

1.8 Packaging, Testing and Debugging:

Finally, the wafer is fabricated and diced into individual chips in a fabrication facility.

- Each chip is then packaged and tested to ensure that it meets all the design specifications and that it functions properly.

- Chips used in Printed Circuit Boards (PCBs) are packaged in Dual In-line Package (DIP), Pin Grid Array (PGA), Ball Grid Array (BGA), and Quad Flat Package (QFP).

- Chips used in Multi-Chip Modules (MCM) are not packaged, since MCMs use bare or naked chips.

Image Source: Wikipedia

Image Source: Wikipedia

2.1 Increasing Interconnect Delay:

- As the fabrication process improves, the interconnect is not scaling at the same rate as the devices.

- Devices are becoming smaller and faster, and interconnect has not kept up with that pace. Almost 60% of a path delay may be due to interconnect.

- One solution to interconnect delay and signal integrity issue is insertion of repeaters in long wires.

- Repeaters are now necessary for most chip level nets.

- Requires advanced planning since area for repeaters must be allocated upfront.

2.2 Increasing Interconnect Area:

- It has been Estimated that a microprocessor die has only 60%-70% of its area covered with active devices.

- 40-30% of the area is needed to accommodate the interconnect that leads to performance degradation.

- In early ICs, a few hundred transistors were interconnected using one layer of metal.

- As the number of transistors grew, the interconnect area increased. However, with the introduction of a second metal layer, the interconnect area decreased.

- Design complexity and the number of metal layers.

- In current designs, with approximately ten million transistors and four to six layers of metal, 40% of the chips area dedicated to its interconnect.

- More metal layers help in reducing the die size, it should be noted that more metal layers but not necessarily mean less interconnect area (after a certain number of layers) due to the space taken up by the vias on the lower layers.

2.3 Increasing Number Of Metal Layers:

- To meet the increasing needs of interconnect, the number of metal layers available for interconnect is increasing.

- Currently, a three layer process is commonly used for most

- designs, while four layer and five layer processes are used mainly for microprocessors.

- As a result, a three dimensional view of the interconnect is necessary.

2.4 Increasing Planning Requirements:

- The most important implication of increasing interconnect delay, area of the die dedicated to interconnect, and a large number of metal layers is that the relative location of devices is very important.

- Physical design considerations have to enter into design at a much earlier phase.

- In fact, functional design should include chip planning.

- This includes two new key steps; block planning and signal planning.

- Block planning : assigns shapes and locations to main functional blocks.

- Signal planning: assign the three dimensional regions through which major busses and signals will be routed.

- Timing should be estimated to verify the validity of the chip plan.

- This plan should be used to create timing constraints for later stages of design.

- Reduces design time, and eliminates human errors.

- Biggest disadvantage is the area used by synthesized blocks take larger areas than hand crafted blocks.

- Depending upon the level of design on which synthesis is introduced, we have two types of

- synthesis.

- Synthesis: The time required to design any block can be reduced if layout can be directly generated or synthesized from a higher level description.

- Logic Synthesis:

- This process converts an HDL description of a block into schematics (circuit description) and then produces its layout.

- Logic synthesis is an established technology for blocks in a chip design, and for complete Application Specific Integrated Circuits (ASICs).

- Not applicable for large regular blocks, such as RAMs, ROMs, PLAs and Datapaths, and complete microprocessor chips for two reasons; speed and area.

- Logic synthesis tools are too slow and too area inefficient to deal with such blocks.

-

High Level Synthesis: This process converts a functional or microarchitectural description into a layout or RTL description.

- In high level synthesis, input is a description which captures only the behavioral aspects

- of the system.

- The synthesis tools form a spectrum. The synthesis system described above can be called general synthesis.

- A more restricted type synthesizes some constrained architectures.

- For example, Digital Signal Processing (DSP) architectures have been successfully synthesized. These synthesis systems are sometimes called Silicon Compilers.

- An even more restricted type of synthesis tools are called Module Generators, which work on smaller size problems.

- The basic idea is to simplify the synthesis task, either by restricting the architecture or restricting the size of the problem.

- In summary, high level synthesis systems provide very good implementations for specialized classes of systems, and they will continue to gain acceptance as they become more generalized.

03. Fabrication Of Integrated Circuits(Video)